近日,中科驭数研究人员前往美国参加了在拉斯维加斯举办的DAC 2019会议(Design, Automation Conference)以及同一地点举办的ICESS 2019 会议(International Conference on Embedded Software and Systems)。

DAC & ICESS : 专用领域的加速器设计成为主流

DAC会议是集成电路设计自动化领域的顶级会议,已被评为中国计算机学会的A类会议,内容涵盖自动驾驶系统,EDA,体系结构设计,嵌入式系统解决方案,物联网,机器学习/人工智能,安全/隐私等多个领域。DAC 2019于美国时间6月2日至6日召开,为期5天,汇聚了全球多个顶级科技公司和研究机构。中科驭数公司的工作《ShuntFlow:An Efficient and Scalable Dataflow Accelerator Architecture for Stream Application》被接收为regular paper,并于6日在本届会议上作口头报告。从今年的报告中我们也发现,专用领域的加速器设计已经逐渐成为主流,DAC录用的文章中,在标题中涉及到“加速”字样的文章高达29篇,是最高频的有效词汇。

本届DAC的keynote也十分精彩,例如Mark Yoseloff博士介绍了自动化技术在赌博业的应用;Galen Hunt博士介绍了微软Azure云服务如何保障十亿级数量的端设备的安全。

Mark Yoseloff博士keynote《Game Changers: How Automation Has Changed the Gaming Industry》

ICESS会议是IEEE旗下嵌入式系统领域会议,目前已成功举办15届,此次也与DAC共同在拉斯维加斯会议中心举办。中科驭数关于区块链方向的工作《BZIP: A Compact Data Memory System for UTXO-based Blockchain》被ICESS录用为regular paper,并于3日在会议上作口头报告。

本届ICESS的keynote邀请到了杜克大学的陈怡然教授,陈教授回顾了实验室近年在嵌入式机器学习系统设计上的科研成果,并分享了科研过程中的宝贵经验。

陈怡然教授keynote 《Embedded Machine Learning Systems Designs: The Lessons We Learned》

ShuntFlow:面向流式数据的高效加速器架构

本工作主要针对流式计算模式,在流式计算,例如金融实时风险监控等应用中,滑动窗聚合(sliding window aggregations,SWAGs)是里面最常见的基本计算模式,然而现在的硬件加速器却面临如何支持任意的滑动窗大小的问题,这在CPU或者GPU上很容易办到,但是要想在FPGA上面使实现的计算核(kernel)支持任意大小的窗口大小是一件比较难的事情,有可能需要重新设计kernel。

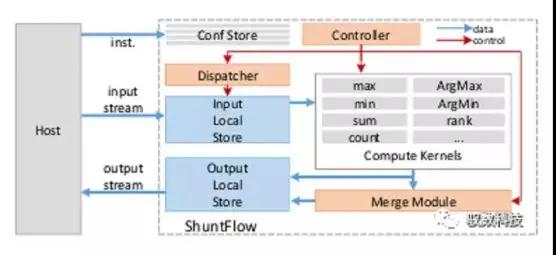

针对这个问题,我们提出了ShuntFlow,一个巧妙的规则使一个刚性实现的计算核(只能支持固定窗口大小)能够支持任意的窗口大小。通过split-merge的方式先将超过加速器处理的SWAGs划分为若干个能够支持处理的sub-SWAGs,再根据特定的merge算法,合并sub-SWAGs得到最后的输出。由于签证问题,本工作的主要作者未能出席会议报告,由目前在杜克大学攻读博后的李冰师姐代为报告。

ShuntFlow现场报告

ShuntFlow架构

BZIP:面向基于UTXO的区块链的数据压缩方法

本工作主要目标是提升区块链系统中节点的交易验签性能,在诸如比特币这样的区块链系统中,验签的重要一步是访问UTXO数据来确定交易是否有效,但是随着UTXO数据的增长,UTXO数据访问速度逐渐成为节点交易验签性能的瓶颈。尽管可以使用缓存等技术,但是受限于DRAM的大小,类似的技术在资源受限的场景下提升有限。

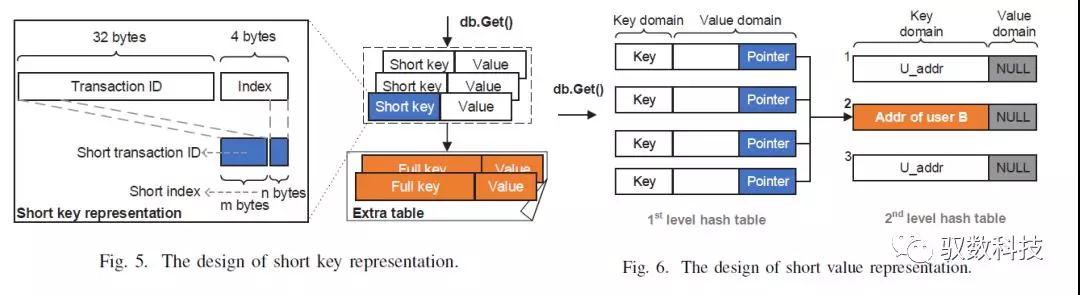

本工作提出了一种专门针对区块链UTXO数据的压缩方法BZIP,一般情况下UTXO数据被存储在key-value数据库中,通过去除UTXO数据中的KEY域和VALUE域的数据冗余,BZIP可以使UTXO数据压缩率达到2.9倍至4.5倍,有效减少了UTXO数据大小,该技术可以在某些应用场景下在交易验签性能上取得数量级的提升。此项工作由实验室的江树浩同学做现场报告。

BZIP现场报告

BZIP系统框架